Hace ya tiempo que tenia ganas de testear estos módulos, no había tenido la oportunidad hasta un par de días. debo mencionar que no soy el autor de la librería y tampoco del demo que les muestro aquí, lo único que realice fue las adecuaciones para trabajar con el PIC18F25K22 y PIC18F46K22, como transmisor y receptor respectivamente, puedes revisar el código original aquí (actualmente ya no esta disponible el repositorio original).

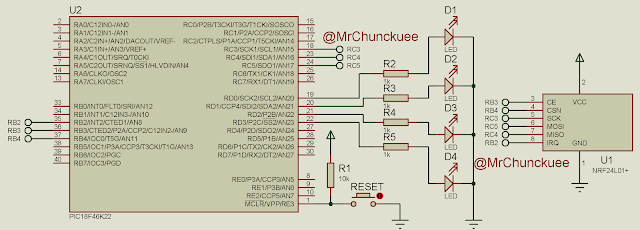

Circuitos:

En la fuente original no se muestra esquemático alguno, pero checando el código, un poco de teoría y las hojas de datos se puede montar el circuito sin ningún problema, otra modificación realizada es el oscilador, la versión original usa un cristal externo de 16MHz, yo he usado el oscilador interno a la misma frecuencia.

A continuación muestro el esquemático que use para el transmisor, dedo comentar que modifique el pin del LED debido a que use el PIC18F25K22 y este no cuenta con un PORTD (en donde estaba originalmente), en cuanto a la alimentación de ambos circuitos es a 3.3 volts.

Como ya mencione he usado el PIC18F46K22 para el receptor, y el circuito usado es el siguiente:

Como el circuito lo monte sobre la protoboard y es notable que los nRF no los podía colocar directamente, realice unas pequeñas adecuaciones con tiras de pines y headers dobles, a continuación las fotos.

Listo los módulos se pueden colocar sin conflicto alguno.

Para el transmisor quedo de la siguiente forma:

El archivo main.c para el transmisor es el siguiente:

Para el receptor quedo de la siguiente forma:

El archivo main.c para el receptor es el siguiente:

Vídeo:

un pequeño video donde muestra los módulos en acción:

Descargas:

Aquí el enlace directo para DESCARGAR los archivos disponibles, también puedes revisar o descargar la información desde mi repositorio en GitHub, si no sabes como descargarlo puedes checar aquí, bueno por el momento es todo si tienes dudas, comentarios, sugerencias, inquietudes, traumas, etc. dejarlas y tratare de responder lo mas pronto posible.

Donaciones:

Si te gusta el contenido o si los recursos te son de utilidad, comparte el enlace en tus redes sociales o sitios donde creas que puede ser de interés y la otra puedes ayudarme con una donación para seguir realizando publicaciones y mejorar el contenido del sitio. También puedes hacer donaciones en especie, ya sea con componentes, tarjetas de desarrollo o herramientas. Ponte en contacto para platicar, o puedes volverte uno de nuestros sponsors.

Pido una retroalimentación avisando cada que un enlace no sirva o tenga errores al momento de abrirlo, así también si una imagen no se ve o no carga, para corregirlo en el menor tiempo posible.

2 Comentarios

Hola.

ResponderEliminarLo primero agradecer tus aportes.

Sabes porque al compilar tu proyecto me salen un monton de warnings de funciones no llamadas y de conversion a datos de tipo mas corto, y en el proyecto original de github no salen siendo practicamente iguales.

Estoy trabajando con mplabx ide ver 2.10 y xc8 v1.34

Gracias

Pues yo estoy usando MPLAB X v3.61 & XC8 v1.42 y tambien me marcan los warnings sobre funciones no llamadas (llegue a casa a compilarlo nuevamente), desconozco el por que el original no los marca, de hecho yo no compile el original directamente cree un proyecto y agregue las librerias. A pesar de eso el demo trabaja bien.

Eliminar